最適化のための μOp キャッシュの基礎知識

ホットスポットでは100%に近い命令が μOp キャッシュでヒットするので、これを理解しておくことは重要です。

予備知識

セットアソシアティブキャッシュの set や way はこちらを参照。

Physically Indexed (PI), Virtually Indexed (VI), Physically Tagged (PT), Virtually Tagged (VT) はこちら。

インクルーシブキャッシュはこちら。

AMD の Op Cache

- Op cache は 32 セット 8 way で構成される。

- 全部で 256 エントリー (32 * 8)

- 各エントリーは最大4マイクロ命令(最大8マクロ命令)を格納する

- よって、Op cache は最大1024マイクロ命令(最大2048マクロ命令)を格納する

- シングルスレッドのホットスポットはこのサイズを超えるべからず

- ふたつの SMT スレッドならば、この半分

- 同じ64バイトアラインのメモリブロックに属する最大8マクロ命令に対応するマイクロ命令がひとつのエントリーに格納される

- 各エントリーは最大8つの32bit即値かオフセット値まで。64bit即値・オフセット値は二つのスロットを消費する

- op cache は IC mode (instruction cache mode) と OC mode (op cache mode) を切り替える

- IC mode から OC mode への遷移は branch target でのみ

- OC mode から IC mode への遷移は、キャッシュミスでフェッチアドレスに対応する op cache エントリーがない場合

- 過剰なモード遷移は IPC によくない影響がありうる (?)

- ホットスポットのコードサイズを op cache の容量に制限すれば、モード遷移の可能性を減らせる

- 容量を超えないことは、特にループアンローリングで重要

- 同じ64バイトアラインのメモリブロックに属する最大8命令が op cache エントリーに格納されるので、ブロックの終わり辺りの命令にジャンプするのはエントリーを非効率にする

- op cache はフラットメモリーモデルでのみ利用される。(64bit か CS のベースが 0 かつ 最大で CS limit の 32bit (?))

Intel の Decoded ICache

AMD の説明とほぼ同じで、日本語ドキュメントもあるので、相違する説明のみ。

- 32 set 8 way

- 各 way は最大6マイクロ命令まで格納する

- 合計は最大1536マイクロ命令

- ひとつの32バイトメモリチャンクに位置する連続するマクロ命令列が最大で3つの way (最大18マイクロ命令)に格納される

- マルチマイクロ命令は way をまたいで分割できない

- 各 way は最大2分岐まで

- MSROM を有効にする命令はひとつの way 全部を消費する

- Decoded ICache は命令キャッシュとITLBにインクルーシブ

- 命令キャッシュで evict(排出) するときは Decoded ICache の対応するラインのみを evict する

- Decoded ICache 全体がフラッシュされる場合がある。ひとつは ITLB のエントリーの eviction

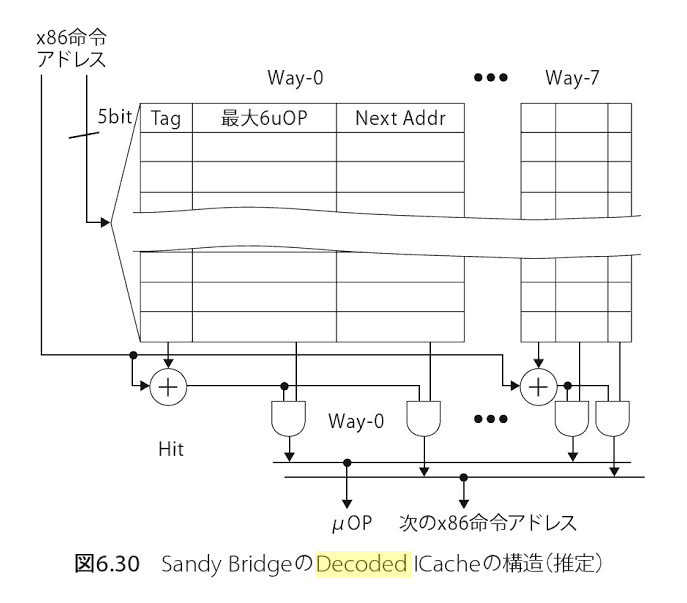

Decoded ICache の推定図

『高性能コンピュータ技術の基礎』 に Hisa Ando 氏の Decoded ICache の構造の推定図が掲載されている。

- way には Next Addr が格納されている

- x86 命令アドレスの 5ビットでインデックスされ、tag が比較されている

疑問点

- VIVT で、仮想アドレスの下位5ビットがインデックス?

- Ryzen の coredump からは下位6ビットが同一のインデックスになっているように推定されなくもないが、0-4 ではなく 1-5 番目のビットでインデックスすることを可能だろうか?

参考文献

- AMD,『Software Optimization Guide for AMD Family 17h Processors』

- Intel,『Intel® 64 and IA-32 Architectures Optimization Reference Manual』

- インテル,『インテル® 64 アーキテクチャーおよび IA-32 アーキテクチャー最適化リファレンス・マニュアル』

- Hisa Ando,『高性能コンピュータ技術の基礎』